Common Source Amplifier

In this amplifier, input signal is applied between gate and source and the amplified output voltage is developed across a load resistor in the drain circuit. Thus, source is the common terminal between the input side and the output side.

Figure 1 gives the circuit of one stage of common source amplifier (CS) Amplifier using n-channel FET and with biasing arrangement. The typical component values are also shown in figure. This circuit is analogous to common emitter amplifier. On using p-channel FET, polarity of supply voltage is reversed. In the circuit of figure 1, Rs-Cs combination provides the self-bias.

Since no current passes through the reverse biased gate-source, the gate current IG is zero. Hence d.c. gate voltage is,

………..(1)

With d.c. drain current set to ID, the dc voltage at the source is,

……….(2)

The gate source voltage is then,

……..(3)

Or, …….(4)

However, quite often capacitor Cs is omitted from the circuit. Then resistor Rs no doubt provides the self-bias (caused by the flow of dc component of drain current) but also provides feedback from output circuit to the input circuit.

Analysis of Common Source Amplifier using FET

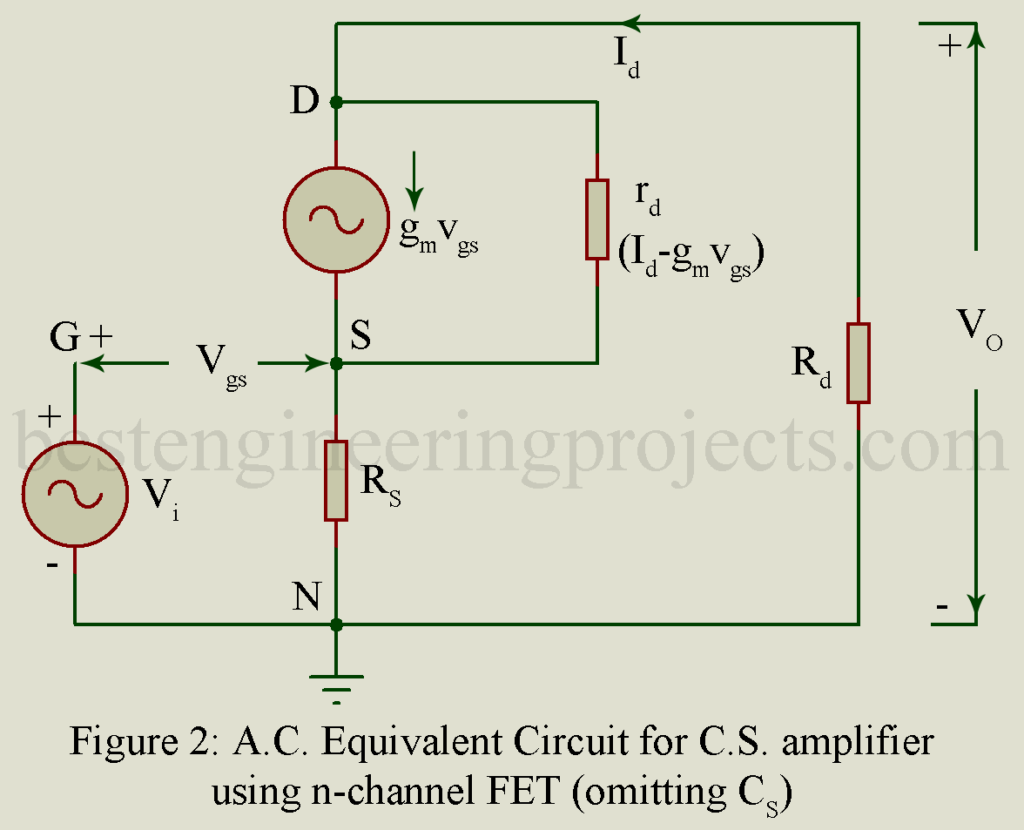

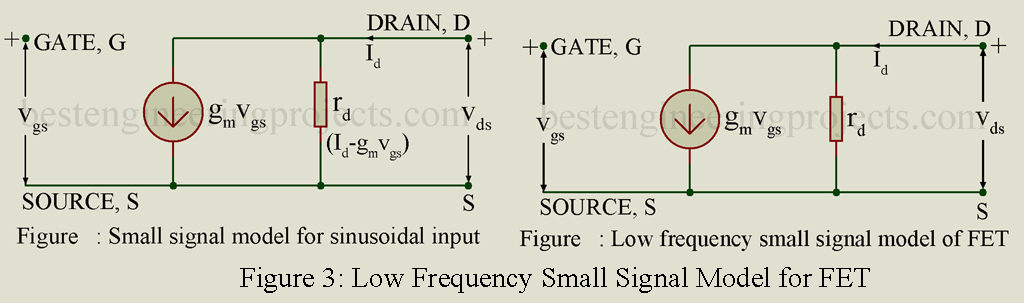

The analysis given below applies to both the n-channel and p-channel common source amplifiers. Figure 2 gives the ac equivalent circuit. Here FET has been replaced by its small signal model of figure 3.

On applying KVL to the output circuit we get

…..(5)

From equivalent circuit of figure 2,

…..(6)

On substituting the value of Vgs from equation (6) in equation (5) we get,

……(7)

The output voltage Vo is developed across the load resistor Rd and is given by,

………(8)

The minus sign associated with V0 as given by equation (8) shows that the output voltage V0 is 1800 out of phase with Vi.

Hence voltage gain,

……..(9)

Since the gate current is zero, input resistance is,

………(10)

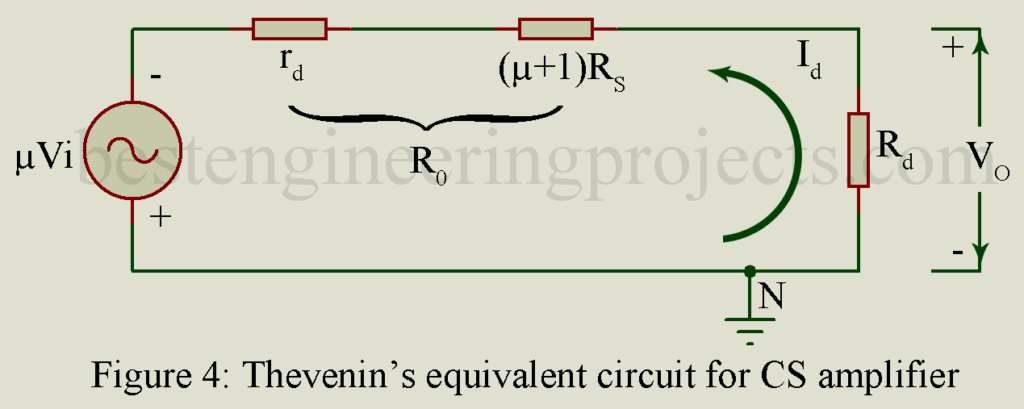

Making use of equation (8), figure 4 gives the equivalent circuit, called the Thevenin’s equivalent circuit, looking from load resistor Rd into the drain-to-ground N. Here (Thevenin’s) equivalent voltage is while its output impedance is,

………(11)

With Rs = 0 In case, Rs is bypassed by a high value capacitor CS i.e. if source S is effectively grounded, then in the above analysis, we may put RS = 0.

Then from equation (9),

……….(12)

Or, ……..(13)

Where,

Output Impedance ………(14)

Numerical Problem on Common Source amplifier using FET

Example 1: A common source amplifier uses FET having dynamic resistance rd = 120 k-ohm and = 20. Calculate the voltage gain and the output resistance Ro for the load resistance Rd equal to : (a) 300 k-ohm (b) 600 k-ohm and (c) 900 k-ohm.

Solution:

Voltage gain,

For Rd = 300 K-ohm,

For Rd = 600 K-ohm,

For Rd = 900 K-ohm,

Example 2: A common source amplifier uses loads resistance and an un-bypassed resistor Rs in the source to ground circuit. the FET has drain resistor

and

. Calculate the voltage gain Av and output resistance Ro for the following values of Rs: (i)

(ii)

(iii)

Solution:

Given that: and

Solution for (i) For :

Solution for (ii) For :

Solution for (iii) For :